PCIe 7.0和8.0标准即将到来, 超高速连接2028年实现

- 2025-08-28 12:26:39

- 141

PCIe总线作为连接x86服务器、PC和笔记本电脑核心处理器与外设的重要方式取得了巨大成功。随着CPU和GPU性能不断提升,PCIe总线速度也在同步增长,每一代都实现带宽翻倍。

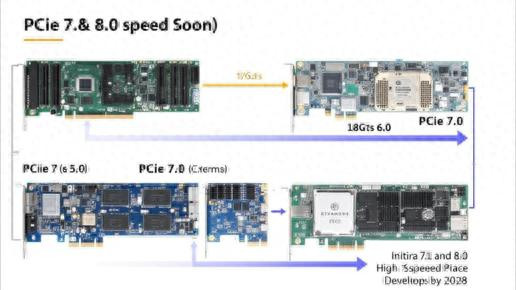

即将到来的PCIe 7.0和8.0标准将带来更高速度,让我们看看它们是如何实现这些性能突破的。

目前PCIe 4.0和5.0标准广泛应用于x86 PC和服务器中连接存储设备等外设,首批6.0版本外设如美光9650 Pro SSD也已问世。由于PCIe标准向后兼容,使用旧版本的外设可以在新版本主机上正常工作。

## PCIe标准基础原理

PCI-SIG是负责PCIe标准开发的行业组织。PCIe总线本质上是外设(如存储驱动器和网络接口卡)与CPU/内存核心复合体之间的串行而非并行连接。它具有多根配对线缆,一根用于接收数据,一根用于传输数据,形成差分信号对,可实现双向传输。两个这样的信号对构成一个通道,PCIe链路可以有1、2、4、8或16个通道。

每个外设都有到CPU的点对点连接,数据通过两部分数据包传输:首先是包含时序信息的标头,然后是数据载荷。这种设计无需单独的时钟时序线。每个通道都有自己的嵌入式时钟,通过参考时钟同步。

在标准FR-4玻璃纤维增强环氧层压板制成的印刷电路板上,PCIe链路长度最多约30厘米,无需中继器或重定时器。

## 性能提升机制

后续PCIe世代通过改变数据编码方案来提高总线速度和承载能力,减少开销。基本性能指标是GTps(每秒千兆传输次数),即每个通道每秒数十亿次传输的数量。每次传输承载的位数根据编码方案而变化。

例如,PCIe 3.0使用8b/10b编码,将8位数据字节转换为10位符号,每8位块增加2位,确保直流平衡且无长串0或1。这增加了25%的开销,PCIe 3.0的原始8 GTps每通道在编码开销后实现约1 GBps的有效带宽。

PCIe 4.0和5.0等后续版本使用128b/130b方案,将开销降至约1.6%,每128位块仅2位。PCIe 5.0的原始32 GTps每通道速率在开销后实现约3.94 GBps。

PCIe 6.0引入了PAM4信号技术,具有4个脉冲幅度电压级别,每个传输信号实现2位而非之前的1位。这提供每通道64 GTps,开销后每通道约7.88 GB/s。

## 未来发展:PCIe 7.0和8.0

PCIe 7.0提供128 GT/s传输率,即每通道128 Gbps,是PCIe 6.0的两倍。除铜连接外,可能还会有基于光互连的版本。PCI-SIG表示它将满足超大规模数据中心800 GbitE、高性能计算、军事/航空航天甚至汽车应用领域的高速数据传输需求。预计PCIe 7.0产品将在规范发布后12-18个月出现,但由于速度极快且成本高昂,可能不会出现在PC级别及以下的产品中。

PCIe 8.0规范的初步工作已经开始,预计将在继续使用PAM4和Flit的同时,将传输率提高到PCIe 7.0的两倍。PCIe 8.0可能需要光链路来克服铜线的频率相关信号损耗。它还可能需要PAM8方案(每信号3位)来提高数据速率,这将需要更好的信噪比检测和错误纠正能力。

有建议认为,PCIe 8.0之后的速度可能达到每通道1 Tbps,约125 GBps,或许会采用PAM16(每信号4位)方案和光互连技术。

从PCIe 4.0开始,PCIe标准每三年更新一次,确保技术持续进步以满足不断增长的性能需求。

Q&A

Q1:PCIe 7.0相比PCIe 6.0有什么提升?

A:PCIe 7.0提供128 GT/s传输率,即每通道128 Gbps,是PCIe 6.0的两倍。它主要面向超大规模数据中心、高性能计算、军事航空航天和汽车应用领域,预计产品将在规范发布后12-18个月出现。

Q2:PAM4信号技术是什么?有什么优势?

A:PAM4信号技术具有4个脉冲幅度电压级别,每个传输信号可以实现2位数据传输,而之前只能传输1位。PCIe 6.0采用这项技术后,实现了每通道64 GTps的传输速率,开销后每通道约7.88 GB/s。

Q3:PCIe 8.0会采用什么新技术?

A:PCIe 8.0预计将传输率提高到PCIe 7.0的两倍,可能需要光链路来克服铜线的信号损耗问题。还可能采用PAM8方案(每信号3位)来提高数据速率,但这需要更好的信噪比检测和错误纠正技术。